# MITSUBISHI LSI DATA BOOK

SUPPLEMENT TO '80 LSI DATA BOOK

All values shown in this catalogue are subject to change for product improvement.

The information, diagrams and all other data included herein are believed to be correct and reliable. However, no responsibility is assumed by Mitsubishi Electric Corporation for their use, nor for any infringements of patents or other rights belonging to third parties which may result from their use.

MELPS and MELCS are registered trademarks of Mitsubishi Electric Corporation.

|    | INDEXES                                            |

|----|----------------------------------------------------|

| 2  | ORDERING INFORMATION AND PACKAGE OUTLINES 2-1~2-15 |

| 3  | GENERAL INFORMATION 3-1~3-8                        |

| 4  | RANDOM-ACCESS MEMORIES                             |

| 5  | READ-ONLY MEMORIES  5-1~5-6                        |

| 6  | MELPS 42 MICROCOMPUTERS 6-1~6-14                   |

| 7  | MELPS 8-48 MICROCOMPUTERS                          |

| 8  | MELPS 86 MICROPROCESSORS 8-1~8-34                  |

| 9  | LSIs FOR PERIPHERAL CIRCUITS  9-1~9-50             |

| 10 | GENERAL-PURPOSE MOS LSIs                           |

| 11 | MICROCOMPUTER SYSTEMS  11-1~11-20                  |

| 12 | MICROCOMPUTER SUPPORT SYSTEMS  12-1~12-6           |

| 13 | MICROCOMPUTER SOFTWARE  13-1~13-8                  |

|    |                                                    |

# PREFACE

Thank you for your continued patronage of Mitsubishi Electric and our semiconductor products.

Semiconductor devices are a mainstay of the burgeoning electronics industry, where they are finding more and more applications, and meeting demands for increased sophistication and diversification of performance and function.

We have already published the 1980 Mitsubishi LSI Data Book, but after then a number of new products are announced, then we have prepared the supplement to the 1980 Mitsubishi LSI Data Book.

This supplement provides detailed specifications of new products, including 16K-bit static RAMs, 32K-bit EPROMs, MELPS 42 single-chip CMOS 4-bit microcomputer, MELPS 8-48 single-chip 8-bit microcomputers, MELPS 86 16-bit microprocessor, board computers and their development and support system, along with additional MOS LSI devices.

We hope you will let us know of any mistakes or omissions that come to your attention, and any suggestions you might have on improving the usefulness of this data book.

January, 1981

Kimio Sato, General Manager Semiconductors Division Mitsubishi Electric Corporation

# MITSUBISHI LSIS CONTENTS

| 1 | INDEXES Index by Function                                                                                                                                                                                                                                                                                  | Page<br>1—                                             | e<br>2        |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------|

| 2 | ORDERING INFORMATION AND PACKAGE OUTLINES  Ordering Information                                                                                                                                                                                                                                            | 2-<br>2-<br>2-<br>2-<br>2-<br>2-1<br>2-1<br>2-1<br>2-1 | 55678901234   |

| 3 | GENERAL INFORMATION  Letter Symbols for the Dynamic parameters  Symbology                                                                                                                                                                                                                                  | 3-<br>3-                                               | 3<br>6        |

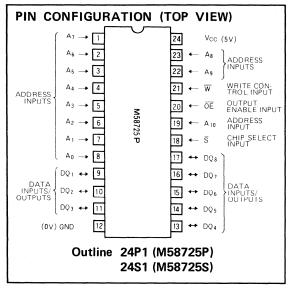

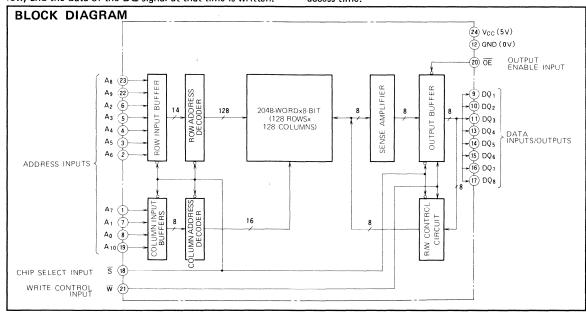

|   | RANDOM-ACCESS MEMORIES M58725P, S; P-15, S-15 16384-Bit (2048-Word by 8-Bit) Static RAM                                                                                                                                                                                                                    | 4—                                                     | 3             |

|   | READ-ONLY MEMORIES  M5L2732K, K-6 32768-Bit (4096-Word by 8-Bit) Erasable and Electrically Reprogrammable                                                                                                                                                                                                  | 5-                                                     | 3             |

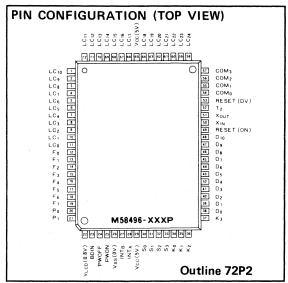

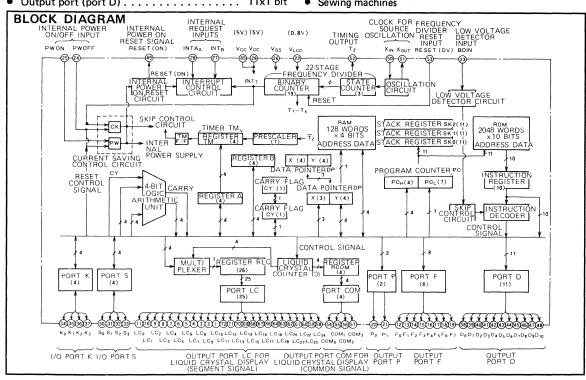

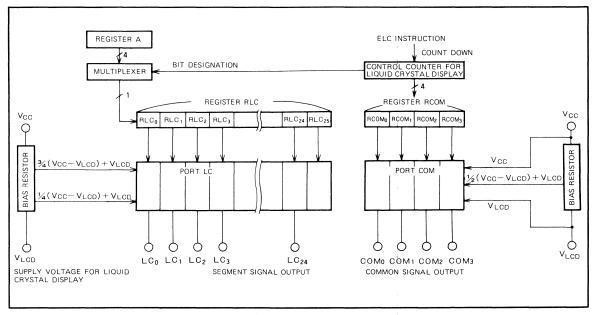

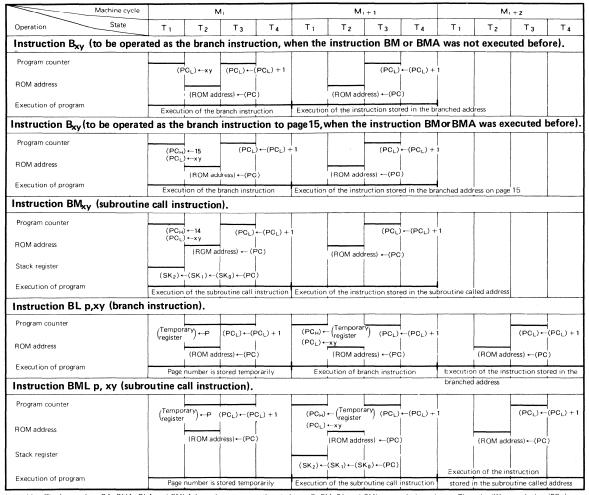

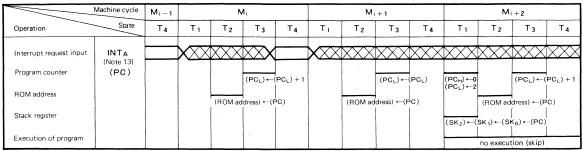

|   | MELPS 42 MICROCOMPUTERS M58496-XXXP Single-Chip 4-Bit CMOS Microcomputer                                                                                                                                                                                                                                   | 6                                                      | 3             |

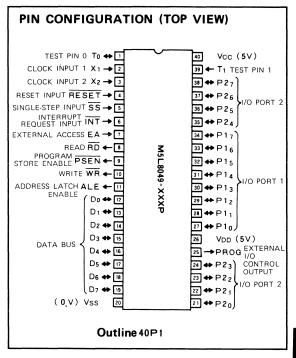

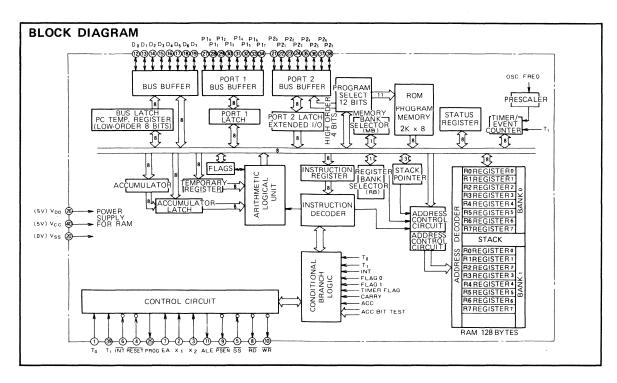

| 7 | MELPS 8-48 MICROCOMPUTERS Function of MELPS 8-48 Microcomputers  M5L8048-XXXP Single-Chip 8-Bit Microcomputer  M5L8748S Single-Chip 8-Bit Microcomputer with EPROM  M5L8049-XXXP, M5L8039P-6 Single-Chip 8-Bit Microcomputers                                                                              | 7-2<br>7-2                                             | ?1<br>?5      |

| 8 | MELPS 86 MICROPROCESSORS M5L8086S 16-Bit Parallel Microprossor                                                                                                                                                                                                                                             | 8                                                      | 3             |

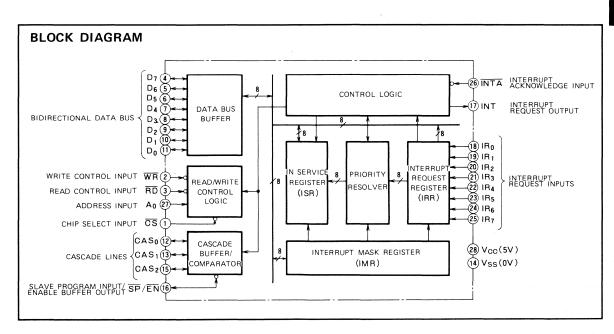

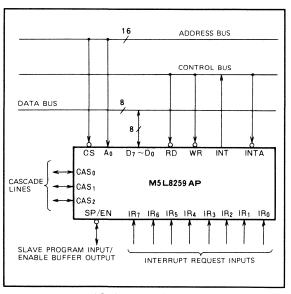

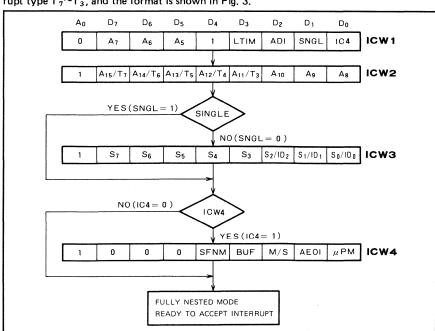

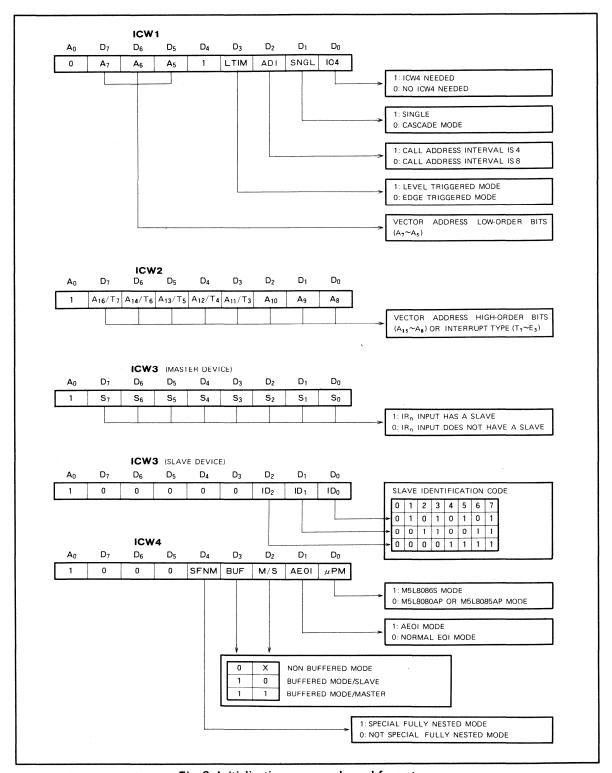

| 9 | LSIs FOR PERIPHERAL CIRCUITS M58990P 8-Bit 8-Channel A-D Converter M5C6847P-1 Video Display Generator M5L8155P 2048-Bit Static RAM with I/O Ports and Timer M5L8156P 2048-Bit Static RAM with I/O Ports and Timer M5L8259AP Programmable Interrupt Controller M5W1791-02P Floppy Disk Formatter/Controller | 9-1<br>9-1<br>9-2<br>9-3                               | 5<br>23<br>31 |

# MITSUBISHI LSIS CONTENTS

| GENERAL-PURPOSE MOS LSIS                                                                                            | Page  |

|---------------------------------------------------------------------------------------------------------------------|-------|

| M50110XP, M50115XP 30- or 120-Function Remote-Control Transmitters                                                  | 10- 3 |

| M50110XP, M50115XP 30- or 120-Function Remote-Control Transmitters                                                  | 10- 9 |

| 11 MICROCOMPUTER SYSTEMS                                                                                            |       |

| MICROCOMPUTER SYSTEMS                                                                                               |       |

| PCA8506 MELSC 85/2 Memory and Parallel I/O Expansion Board                                                          | 11- 3 |

| PCA8506 MELSC 85/2 Memory and Parallel I/O Expansion Board PCA8507 MELCS 85/2 Memory and Serial I/O Expansion Board | 11- 7 |

| PCA8520G01, G02 MELCS 85/3 Voice Generating Single-Board Computer                                                   | 11-11 |

| PCA8540G01, G02 MELCS 85/2 Color TV Display Single-Board Computer                                                   | 11-15 |

| 12 MICROCOMPUTER SUPPORT SYSTEMS                                                                                    |       |

| MICROCOMPUTER SUPPORT SYSTEMS                                                                                       |       |

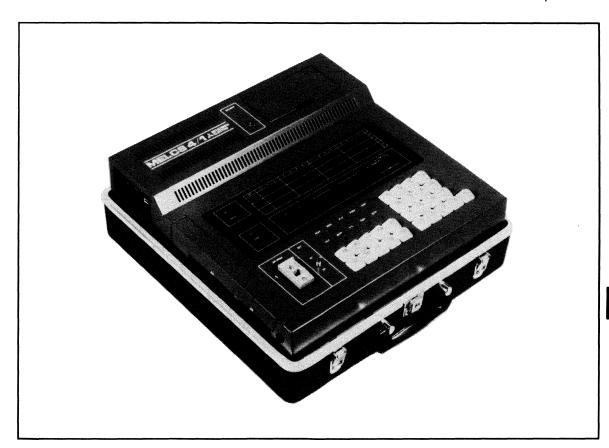

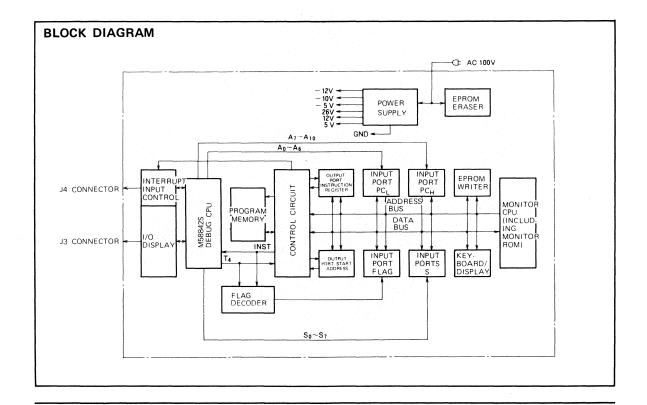

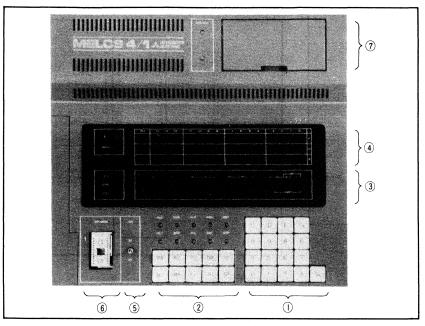

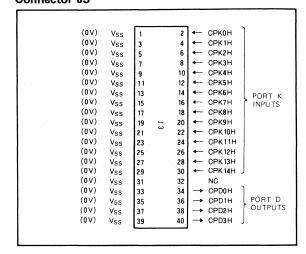

| PC0400 MELCS 4/1 Portable Development Support System                                                                | 12- 3 |

| 13 MICROCOMPUTER SOFTWARE                                                                                           |       |

| MEI DE 42 Seferare Const Assembler                                                                                  | 40 0  |

| MELPS 42 Software Cross Assembler                                                                                   | 13- 3 |

| MELPS 42 Software Paper-Tape Generation Program for PROM Writers                                                    | 13— 7 |

# INDEXES

## MITSUBISHI LSIs **INDEX BY FUNCTION**

| Type<br>(Note 1)            |          | Former<br>designation | Circuit function and organization                               | Application notes                                                               | Structure<br>(Note 2) | Ambient<br>operating<br>temp.<br>Ta(°C) |

|-----------------------------|----------|-----------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------|-----------------------------------------|

| tatic RAMs                  |          |                       |                                                                 |                                                                                 |                       |                                         |

| M58725P, S-19<br>M58725P, S | 5 *<br>* | · <del>-</del>        | 16384-Bit(2048×8) Static RAM                                    | Power down by $\overline{\text{CS}}$                                            | N,Si,ED               | 0~70                                    |

| ield-Programn               | nable    | ROMs (EP              | PROMs)                                                          |                                                                                 |                       |                                         |

| M5L2732K<br>M5L2732K-6      | *        | _                     | 32768-Bit (4096×8) Erasable and Electrically Reprogrammable ROM | Electrical programming ultraviolet erasing                                      | N,Si,FA               | 0~70                                    |

| Single-Chip Mi              | croco    | omputers              |                                                                 |                                                                                 |                       |                                         |

| M58496-XXXP                 | **       |                       | Single-Chip 4-Bit CMOS Microcomputer                            | 77 instructions mask-prog ROM 1K-word by 10-Bit, RAM 128-word by 4-Bit          | C,AI                  | _10~70                                  |

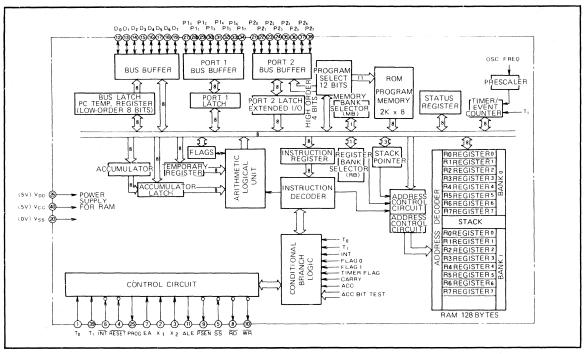

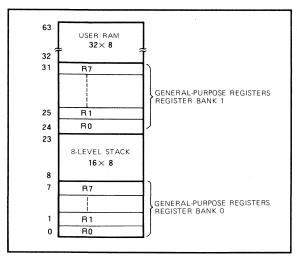

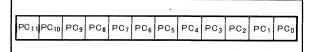

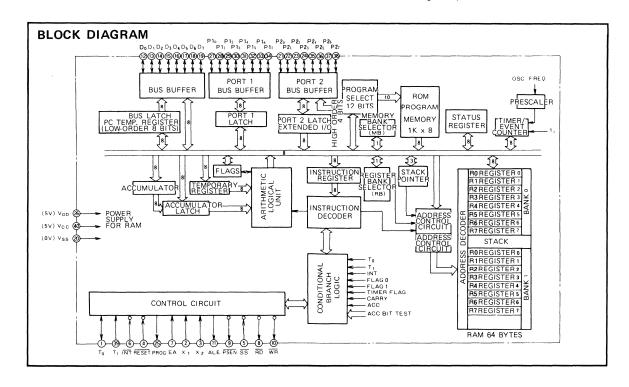

| M5L8048-XXX                 | P *      | _                     | Single-Chip 8-Bit Microcomputer                                 | 96 instructions mask-prog ROM 1K-word<br>by 8-bit RAM 64-word by 8-bit          | N,Si,ED               | 0~70                                    |

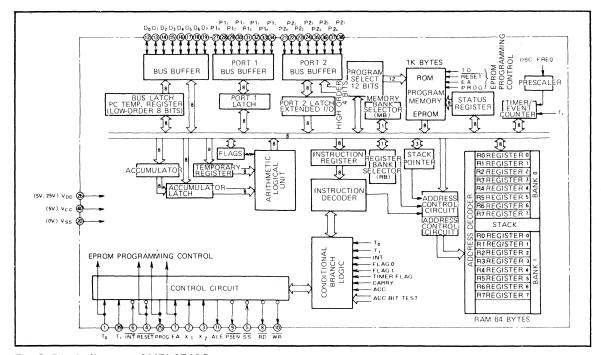

| M5L8049-XXX                 | P *      |                       | Single-Chip 8-Bit Microcomputer                                 | 96 instructions mask-prog ROM 2K-word<br>by 8-bit RAM 128-word by 8-bit         | N,Si,ED               | 0~70                                    |

| M5L8039P -6                 | *        |                       | Single-Chip 8-Bit Microcomputer                                 | 96 instructions RAM 128-word by 8-bit                                           | N,Si,ED               | 0~70                                    |

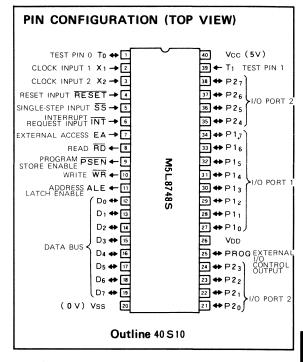

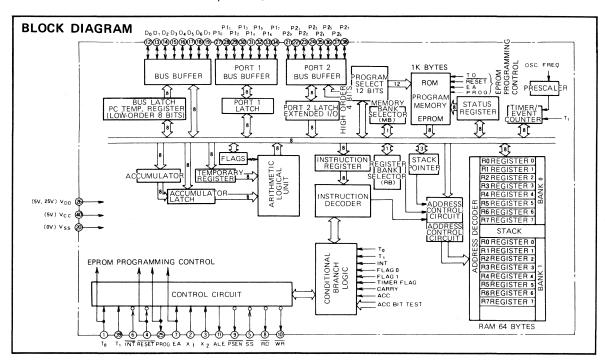

| M5L8748S                    | **       |                       | Single-Chip 8-Bit Microcomputer with EPROM                      | 96 instructions EPROM 1K-word<br>by 8-bit RAM 64-word by 8-bit                  | N.Si.ED               | 0~70                                    |

| /licroprocessor             | 's       |                       |                                                                 |                                                                                 |                       |                                         |

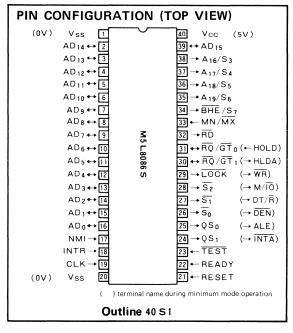

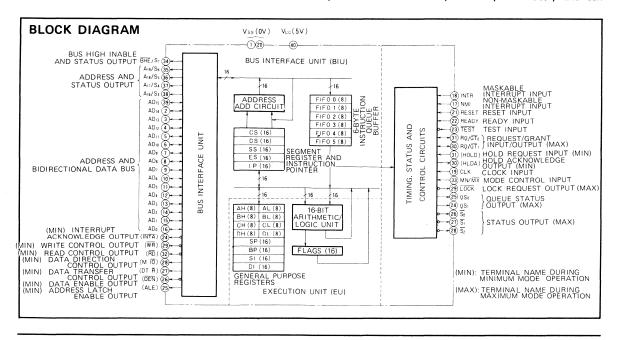

| M5L8086S                    | **       |                       | 16-Bit Microprocessor                                           | 97 instructions 1M-Byte direct access 16-bit CPU                                | N,Si,ED               | 0~70                                    |

| .Sls for Periph             | eral (   | Circuits              |                                                                 |                                                                                 |                       |                                         |

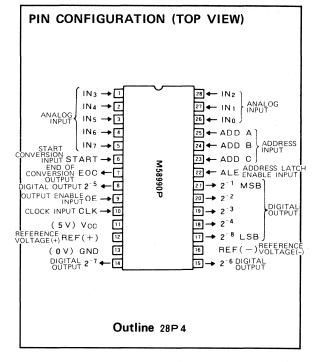

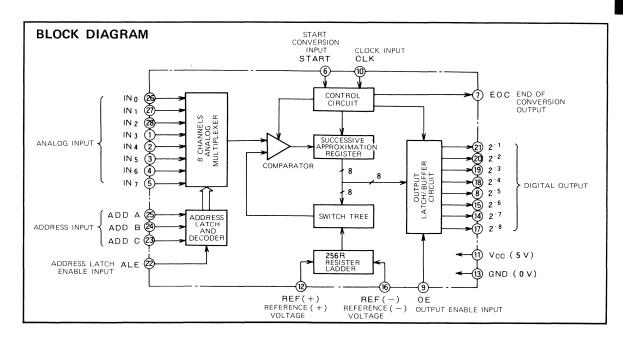

| M58990P                     | **       | _                     | 8-Bit, 8-channel A-D Converter                                  |                                                                                 | C,Si                  | 0~70                                    |

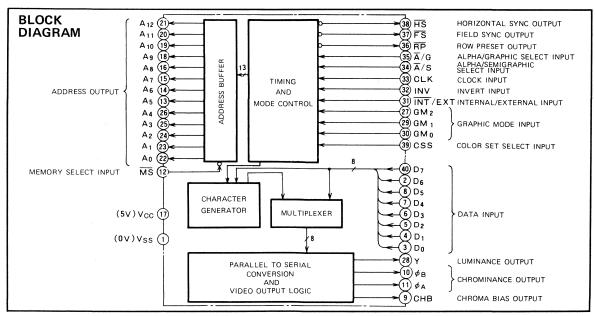

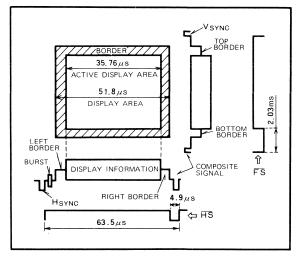

| M5C6847P-1                  | *        | _                     | Video Display Generator                                         | 4 different alphanumeric and 8 different graphic display modes                  | N,Si,ED               | 0~70                                    |

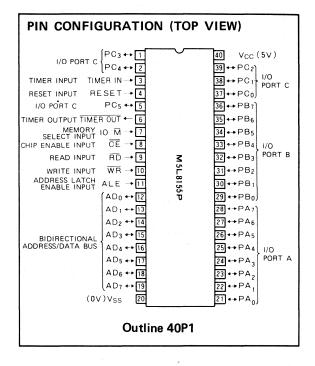

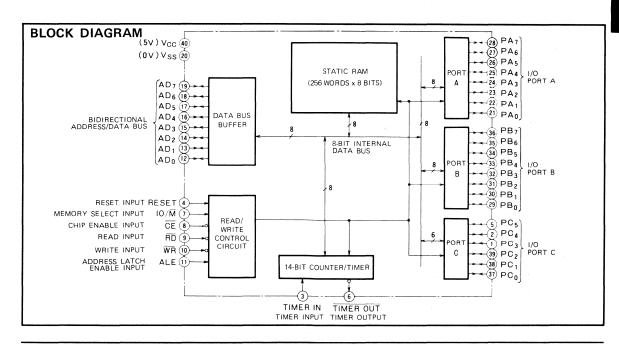

| M5L8355P                    | *        |                       | 2048-Bit Static RAM with I/O Ports and Timer                    | 256-word×8-Bit RAM with 22 I/O low pins and 14-Bits counter/timer CE=low active | N,Si,ED               | 0~70                                    |

| M5L8156P                    | *        | alexander.            | 2048-Bit Static RAM with I/O Ports and Timer                    | 256 word×8-Bit RAM with 22 I/O pins and 14-Bit counter/timer CE≈high active     | N,Si,ED               | 0~70                                    |

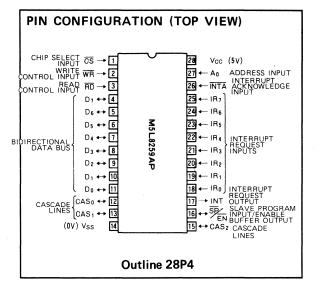

| M5L8259AP                   | *        | administra            | Programmable Interrupt Controller                               | 8 vectored priority interrupts                                                  | N,Si,ED               | 0~70                                    |

| M5W1791-02P                 | **       | Velocies              | Floppy Disk Formatter/Controller                                | Single and double density formats                                               | N,Si,ED               | 0~70                                    |

| General Purpos              | e M      | OS LSIs               |                                                                 |                                                                                 |                       |                                         |

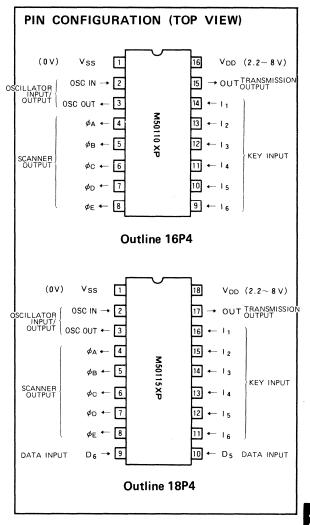

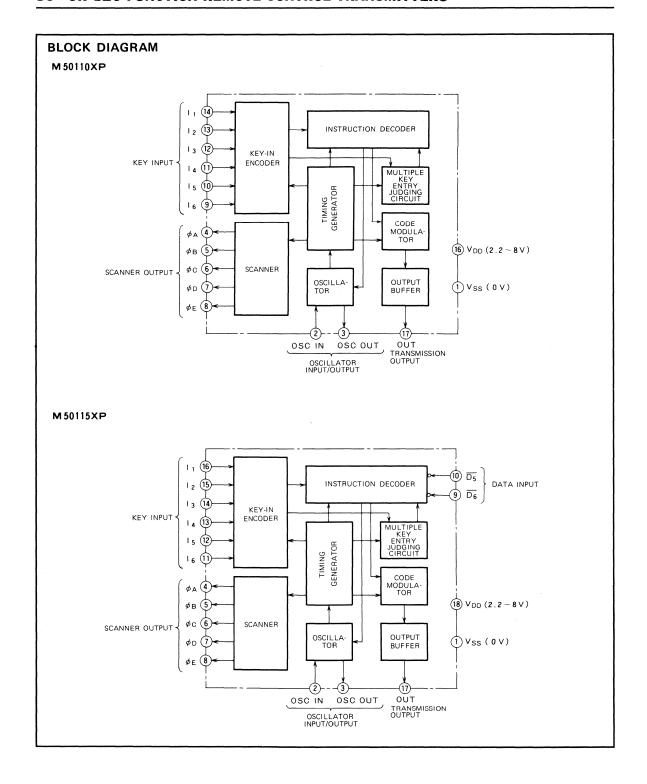

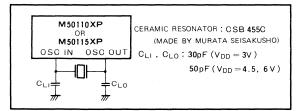

| M50110XP                    | *        |                       | 30-Function Remete-Control Transmitter                          |                                                                                 | C, Al                 | -30~70                                  |

| M50115XP                    | *        | _                     | 120-Function Remote-Control Transmitter                         |                                                                                 | C, Al                 | 30~70                                   |

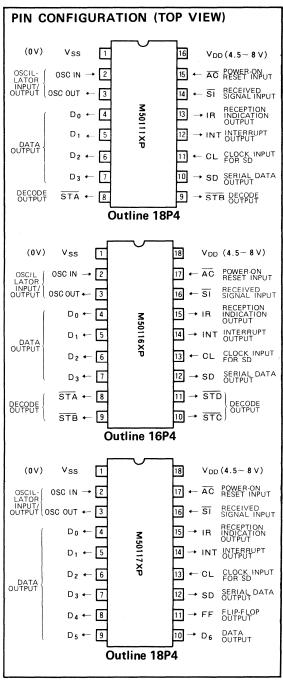

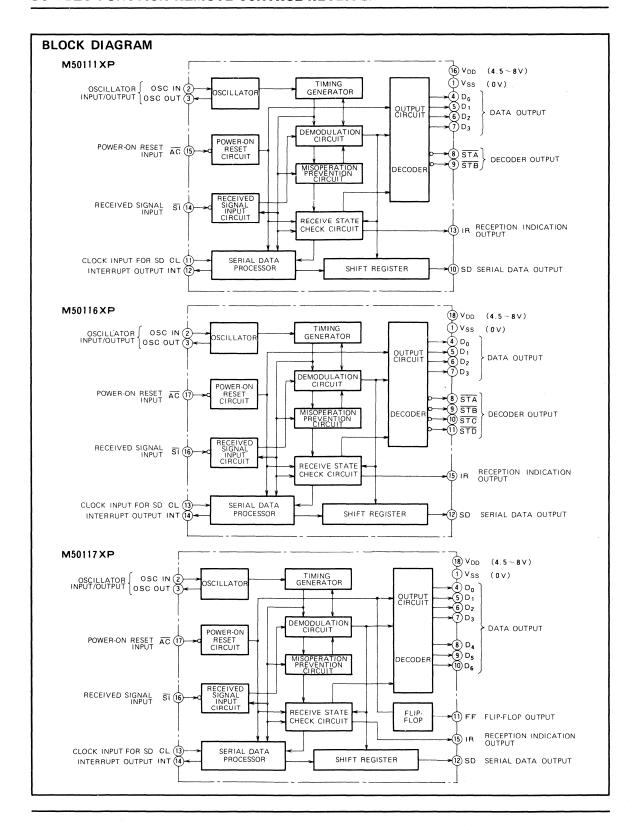

| M50111XP                    | *        | Anna                  | 120-Function Remote-Control Receiver                            |                                                                                 | C, Al                 | —30 ~ 70                                |

| M50116XP                    | *        |                       | 120-Function Remote-Control Receiver                            |                                                                                 | C, Al                 | -30~70                                  |

| M50117XP                    | *        |                       | 120-Function Receiver Remote-Control                            |                                                                                 | C, Al                 | -30~70                                  |

# MITSUBISHI LSIS INDEX BY FUNCTION

| S                                     | upply voltage |                        |                 | CIS I                                          |                                     | Electric                       | al chara                      | cteristics                      |                                | 1                  | Interchang         | eable products | -    |

|---------------------------------------|---------------|------------------------|-----------------|------------------------------------------------|-------------------------------------|--------------------------------|-------------------------------|---------------------------------|--------------------------------|--------------------|--------------------|----------------|------|

| V <sub>DD</sub>                       | Vcc           | V <sub>SS</sub><br>GND | V <sub>BB</sub> | Clock voltage $V_1(\phi)$                      | Typ pwr<br>dissi-<br>pasion<br>(mW) | Max.<br>access<br>time<br>(ns) | Max.<br>cycle<br>time<br>(ns) | Max.<br>fre-<br>quency<br>(MHz) | TTL<br>com-<br>pati-<br>bility | Package<br>(Note3) | Mfr.               | Туре           | Page |

|                                       |               |                        |                 |                                                |                                     | -                              |                               |                                 | - <del></del>                  |                    |                    |                |      |

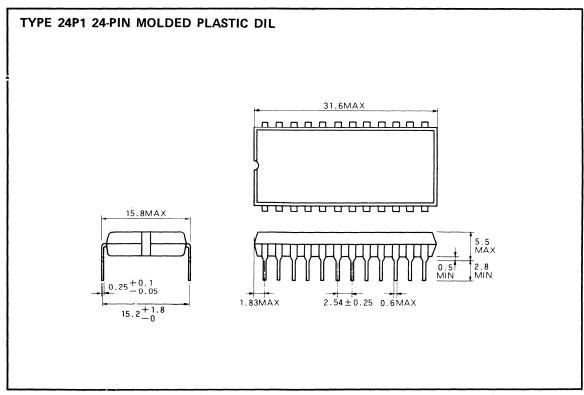

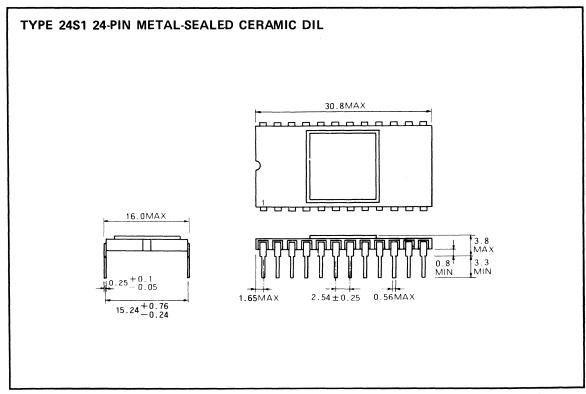

|                                       | E\/ : 40**    | 011                    |                 |                                                | 200                                 | 150                            | 150                           |                                 |                                | 24P1               | -                  | TMS4016-15     | T    |

|                                       | 5V±10%        | 0V                     | _               | , <del>-</del>                                 | 200                                 | 200                            | 200                           |                                 | Yes                            | 24S1               | TI                 | TMS4016        | 4-3  |

|                                       |               |                        |                 |                                                |                                     |                                |                               |                                 |                                |                    |                    | - 1            |      |

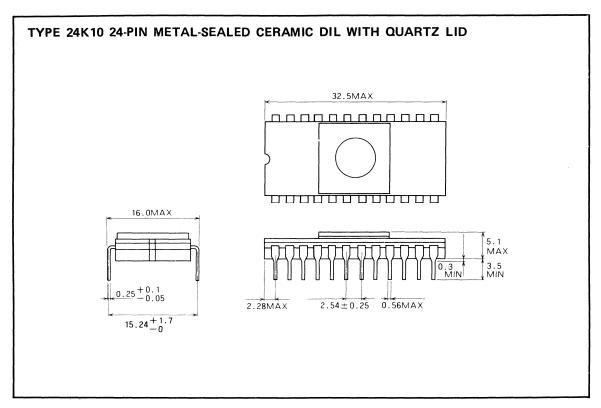

|                                       | EV 1 FO       | 0) (                   |                 |                                                | 400                                 | 450                            | _                             |                                 |                                | 24810              | INITE              | D2732          | T .  |

|                                       | 5V±5%         | 0V                     | _               |                                                | 400                                 | 550                            | _                             | _                               | Yes                            | 24K10              | INTEL              | D2732-6        | 5-3  |

|                                       |               |                        |                 |                                                |                                     |                                |                               |                                 |                                |                    |                    |                | - 1  |

| - 1                                   | 5V±5%         | 0V                     |                 |                                                | 5                                   |                                | 7700                          | 4.2                             | Yes                            | 72P2               | _                  |                | 6-3  |

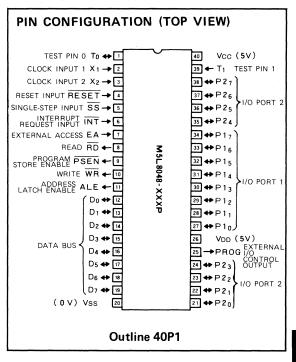

| -                                     | 5V±10%        | 0V                     | _               |                                                | 325                                 |                                | _                             | 6                               | Yes                            | 40P1               | INTEL              | P8048          | 7-21 |

| _                                     | 5V±10%        | 0V                     | _               | _                                              | 500                                 |                                |                               | - 6                             | Yes                            | 40P1               | INTEL              | P8049          | 7-33 |

| _                                     | 5V±10%        | 0V                     | -               | _                                              | 500                                 | _                              | _                             | 6                               | Yes                            | 40P1               | INTEL              | P8039          | 7-33 |

| _                                     | 5V±5%         | 0V                     | _               | _                                              | 500                                 | _                              | _                             | 6                               | Yes                            | 40S10              | INTEL              | C8748          | 7-25 |

| · · · · · · · · · · · · · · · · · · · |               |                        | 1.              |                                                |                                     |                                |                               |                                 |                                |                    |                    |                |      |

| _                                     | 5V±10%        | 0V                     | _               | 3.9V                                           | 1375                                | _                              | -                             | 5                               | Yes                            | 40S1               | INTEL              | C8086          | 8-3  |

|                                       |               |                        |                 |                                                |                                     |                                |                               |                                 |                                | l                  |                    |                |      |

|                                       |               | 01.                    |                 |                                                |                                     |                                | 1                             |                                 |                                | 2001               | NC                 | 1000000        |      |

|                                       | 5V±10%        | 0V                     | _               |                                                |                                     | -                              | _                             | _                               | Yes                            | 28P4               | NS                 | ADC0808        | 9-3  |

| _                                     | 5V±5%         | 0V                     | _               | 2.4V                                           | 500                                 | _                              | _                             | 3.85                            | Yes                            | 40P1               | MOTOROLA           | MC6847-1       | 9-5  |

| _                                     | 5V±5%         | 0V                     | water           | _                                              | 500                                 | _                              |                               |                                 | Yes                            | 40P1               | INTEL              | P8155          | 9-15 |

| _                                     | 5V±5%         | 0V                     | _               |                                                | 500                                 |                                | _                             | _                               | Yes                            | 40P1               | INTEL              | P8156          | 9-23 |

| _                                     | 5V±10%        | 0V                     | _               | _                                              | 275                                 | _                              | _                             | -                               | Yes                            | 28P4               | INTEL              | P8259A         | 9-31 |

|                                       | 5V±5%         | 0V                     | _               | -                                              | -                                   | 300                            | _                             |                                 | Yes                            | 40P1               | WESTERN<br>DIGITAL | FD1791-02B     | 9-45 |

|                                       |               |                        |                 |                                                | •                                   |                                |                               |                                 |                                |                    |                    |                |      |

| .2~8V                                 | Acres.        | 0V                     | _               | _                                              | _                                   | _                              | _                             | _                               | _                              | 16P4               | _                  | _              | 10-3 |

| .2~8V                                 | _             | 0V                     | _               | _                                              | _                                   | - Marine                       | _                             |                                 |                                | 18P4               | _                  |                | 10-3 |

| .5~8V                                 | roma.         | 0V                     | _               | _                                              | THEORY                              | _                              | _                             | _                               | Yes                            | 16P4               | _                  |                | 10-9 |

| .4~8V                                 | _             | 0V                     |                 |                                                |                                     |                                | _                             | _                               | Yes                            | 18P4               | _                  | _              | 10-9 |

| .5~8V                                 | _             | 0V                     |                 | _                                              |                                     | _                              | _                             |                                 | Yes                            | 18P4               | _                  |                | 10-9 |

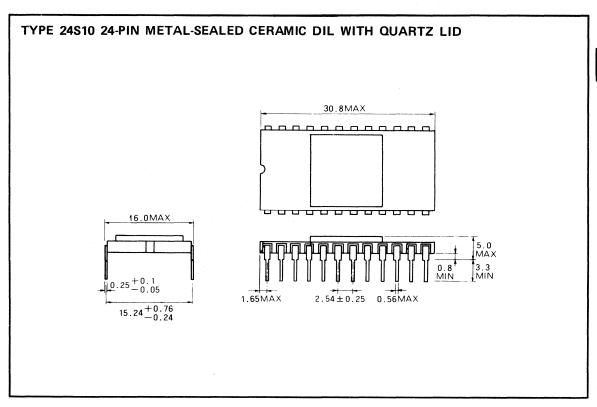

|                                       |               | 0V 24 S                |                 | —— Num<br>—— Pack<br>K = G<br>—— Pack<br>1 = D | der of pins<br>age structur         | e<br>ceramic. F<br>in.         | <sup>2</sup> =Molded          |                                 | S=Meta                         | al-sealed cer      | amic               |                | 10-  |

## **INDEX BY FUNCTION**

| Туре    | Function | Application notes | Memory  | capacity<br>ROM | I/O<br>port | Ambient operating temp | Supply<br>voltage | Dimensions<br>(I×w×h) | Page |

|---------|----------|-------------------|---------|-----------------|-------------|------------------------|-------------------|-----------------------|------|

| (Note4) |          |                   | (bytes) | (bytes)         | (bits)      | Ta (°C)                | (V)               | (mm)                  |      |

#### Microcomputer System

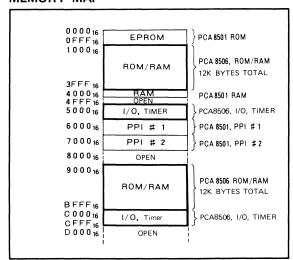

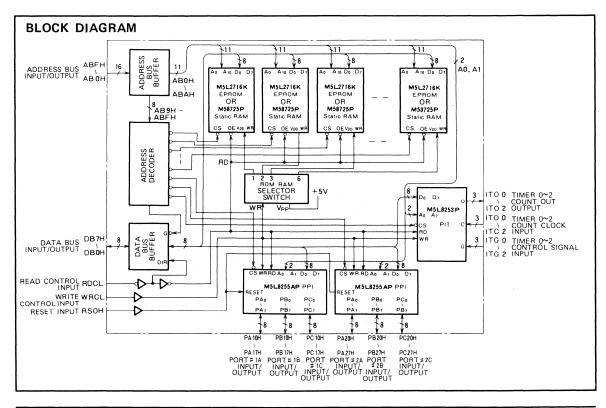

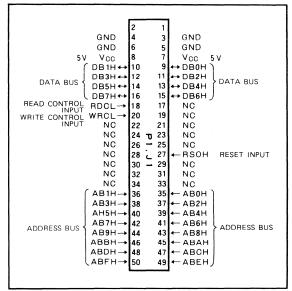

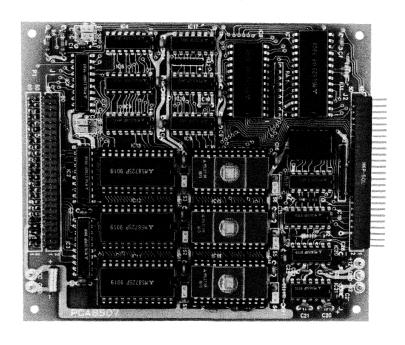

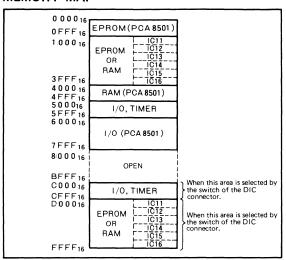

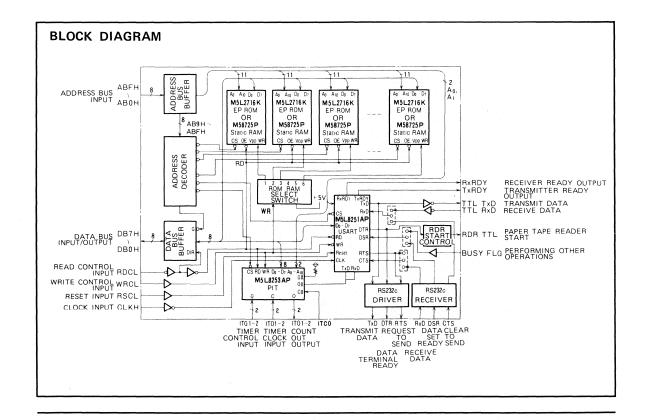

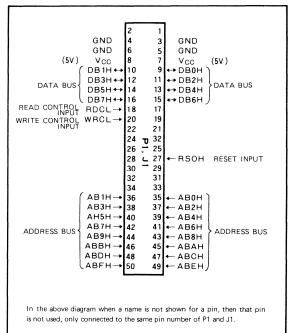

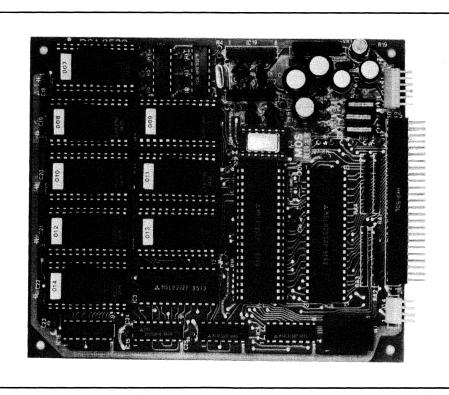

| PCA8506 *                  | MELCS 85/2 Memory and<br>Parallel I/O Expansion Board  | For PCA8501 PCA8540            | 12K(I | Note1)         | 48            | 0~55 | 5        | 125×145×17 | 11-3  |

|----------------------------|--------------------------------------------------------|--------------------------------|-------|----------------|---------------|------|----------|------------|-------|

| PCA8507 *                  | MELCS 85/2 Memory and<br>Serial I/O Expansion Board    | For PCA8501,PCA8540            | 12K(N | Note1)         | 1<br>(serial) | 0~55 | 12.5,—12 | 125×145×17 | 11-7  |

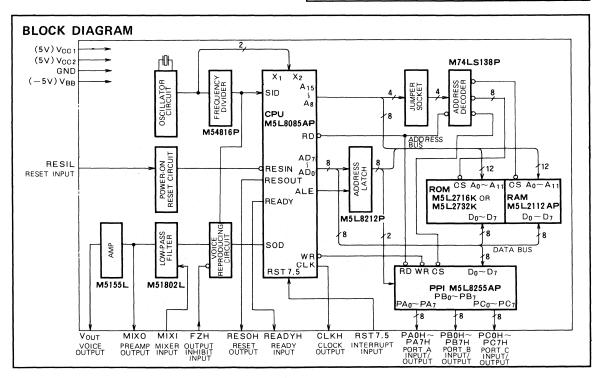

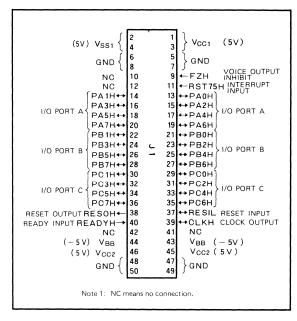

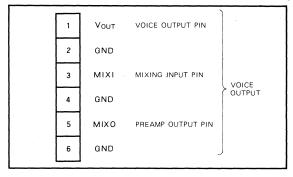

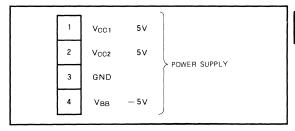

| PCA8520G01 * PCA8520G02 *  | MELCS 85/3 Voice Generating Single-Board Computer      | Using M5L8085AP                | 256   | 16K<br>(Note2) | 24            | 0~55 | 5,—5     | 125×145×20 | 11-11 |

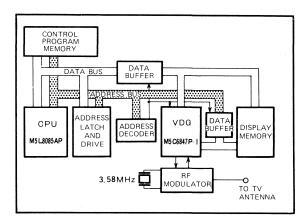

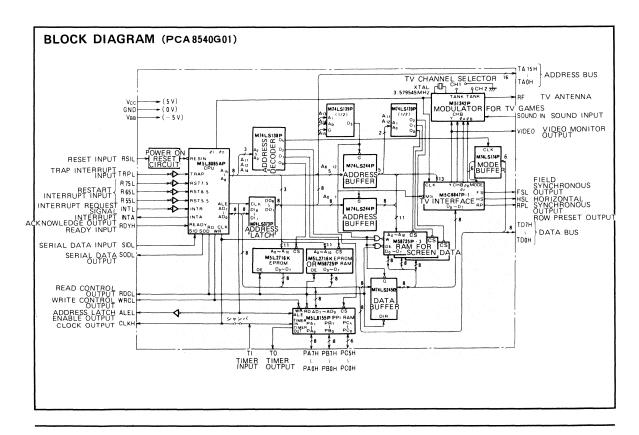

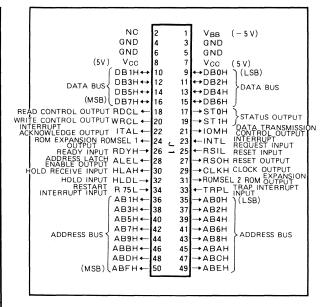

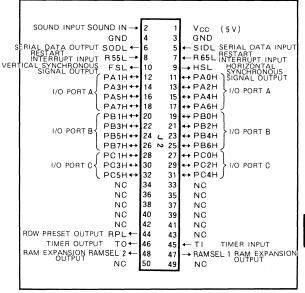

| PCA8540G01*<br>PCA8540G02* | MELCS 85/2 Color TV Dis-<br>play Single-Board Computer | Using M5L8085AP and M5C6847P-1 | 256   | 4K<br>(Note3)  | 22            | 5~40 | 5.—5     | 125×145×20 | 11-15 |

Note 1: The standard product contains neither M5L2716K 2K-byte EPROMs or M58725P 2K-byte static RAMs. 2: The PCA8520G01 does not contains M5L2716K EPROMs. The PCA8520G01 contains standard voice stored in eight M5L2716K EPROMs. 3: The standard product contains no M5L2716K EPROMs.

#### Microcomputer Support Systems

#### **MELPS Software**

| Program                                                    | Program code number | Normal shipping media | Source language                |

|------------------------------------------------------------|---------------------|-----------------------|--------------------------------|

| MELPS 42 Cross Assembler                                   | GB1AS0010           | Magnetic tape         | FORTRAN<br>(part in assembler) |

| MELPS 42 Paper-Tape Generation<br>Program for PROM Writers | GB1SP0006           | Magnetic tape         | FORTRAN<br>(part in assembler) |

<sup>4: \*:</sup> New Product;

# **ORDERING INFORMATION AND PACKAGE OUTLINES**

## **ORDERING INFORMATION**

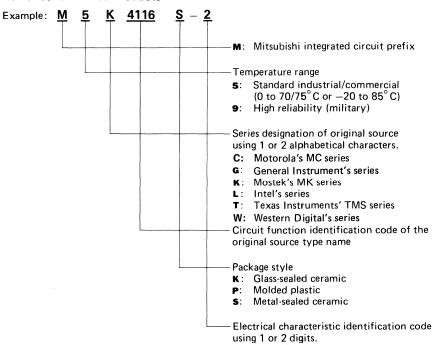

#### **FUNCTION CODE**

Mitsubishi integrated circuits may be ordered using the following simplified alphanumeric type-codes which define the function of the ICs and the package style.

#### For Mitsubishi Original Products

# **ORDERING INFORMATION**

#### For Second Source Products

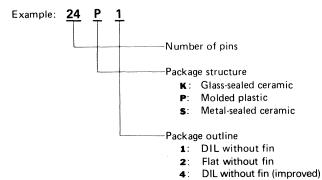

### PACKAGE CODE

Package style may be specified by using the following simplified alphanumeric code.

#

# **GENERAL INFORMATION**

3

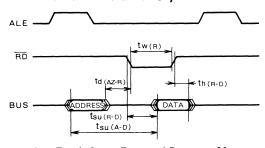

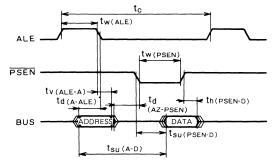

## LETTER SYMBOLS FOR THE DYNAMIC PARAMETERS

#### 1. INTRODUCTION

A system of letter symbols to be used to represent the dynamic parameters of intergrated circuit memories and other sequential circuits especially for single-chip microcomputers, microprocessors and LSIs for pheripheral circuits has been discussed internationally in the TC47 of the International Electrotechnical Committee (IEC). Finally the IEC has decided on the meeting of TC47 in February 1980 that this system of letter symbols will be a Central Office document and circulated to all countries to vote which means this system of letter symbols will be a international standard.

The system is applied in this LSI data book for the new products only. Future editions of this data book will be applied this system. The IEC document which describes "Letter symbols for dynamic parameters of sequential integrated circuits, including memories" is introduced below. In this data book, the dynamic parameters in the IEC document are applied to timing requirements and switching characteristics.

#### 2. LETTER SYMBOLS

The system of letter symbols outlined in this document enables symbols to be generated for the dynamic parameters of complex sequential circuits, including memories, and also allows these symbols to be abbreviated to simple mnemonic symbols when no ambiguity is likely to arise.

#### 2.1. General Form

The dynamic parameters are represented by a general symbol of the form:-

where:

Subscript A indicates the type of dynamic parameter being represented, for example; cycle

time, setup time, enable time, etc.

Subscript B indicates the name of the signal or terminal for which a change of state or level (or establishment of a state or level) constitutes a signal event assumed to occur first, that is, at the beginning of the time interval. If this event actually occurs last, that is, at the end of the time interval, the value of the time interval is negative.

Subscript C indicates the direction of the transition and/or the final state or level of the signal represented by B. When two letters are used, the initial state or level is also indicated.

Subscript D indicates the name of the signal or terminal for which a change of state or level (or establishment of a state or level) constitutes a signal event assumed to occur last, that is, at the end of the time interval. If this event actually occurs first, that is, at the beginning of the time interval, the

value of the time interval is negative.

Subscript E indicates the direction of the transition and/or the final state or level of the signal represented by D. When two letters are used, the initial state or level is also indicated.

Subscript F indicates additional information such as mode of operation, test conditions, etc.

Note 1: Subscripts A to F may each consists of one or more letters.

- 2: Subscripts D and E are not used for transition times.

- 3: The "-" in the symbol (1) above is used to indicate "to"; hence the symbol represents the time interval from signal event B occurring to signal event D occurring, and it is important to note that this convention is used for all dynamic parameters including hold times. Where no misunderstanding can occur the hyphen may be omitted.

#### 2.2. Abbreviated Form

The general symbol given above may be abbreviated when no misunderstanding is likely to arise. For example to:

t<sub>A(B-D)</sub>

or tA(B)

or t<sub>A(D)</sub> - often used for hold times

or t<sub>AF</sub> - no brackets are used in this case

or t<sub>A</sub>

or  $t_{BC-DE}$  — often used for unclassified time intervals

#### 2.3. Allocation of Subscripts

In allocating letter symbols for the subscripts, the most commonly used subscripts are given single letters where practicable and those less commonly used are designated by up to three letters. As far as possible, some form of mnemonic representation is used. Longer letter symbols may be used for specialised signals or terminals if this aids understanding.

# 3. SUBSCRIPT A (For Type of Dynamic Parameter)

The subscript A represents the type of dynamic parameter to be designated by the symbol and, for memories, the parameters may be divided into two classes:

a) those that are timing requirements for the memory and

### LETTER SYMBOLS FOR THE DYNAMIC PARAMETERS

b) those that are characteristics of the memory. The letter symbols so far proposed for memory circuits are listed in sub-clauses 3.1 and 3.2 below.

All subscripts A should be in lower-case.

#### 3.1. Timing Requirements

The letter symbols for the timing requirements of semiconductor memories are as follows:

| Term                                    | Subscript |

|-----------------------------------------|-----------|

| Cycle time                              | С         |

| Time interval between two signal events | d         |

| Fall time                               | f         |

| Hold time                               | h         |

| Precharging time                        | рс        |

| Rise time                               | r         |

| Recovery time                           | rec       |

| Refresh time interval                   | rf        |

| Setup time                              | su        |

| Transition time                         | t         |

| Pulse duration (width)                  | w         |

#### 3.2. Characteristics

The letter symbols for the dynamic characteristics of semiconductor memories are as follows:

| Characteristic   | Subscript |

|------------------|-----------|

| Access time      | а         |

| Disable time     | dis       |

| Enable time      | en        |

| Propagation time | р         |

| Recovery time    | rec       |

| Transition time  | t         |

| Valid time       | v         |

Note: Recovery time for use as a characteristic is limited to sense recovery time

# 4. SUBSCRIPTS B AND D (For Signal Name or Terminal Name)

The letter symbols for the signal name or the name of the terminal are as given below.

All subscripts B and D should be in upper-case.

| Signal or terminal    | Subscript |

|-----------------------|-----------|

| Address               | Α         |

| Clock                 | C         |

| Column address        | CA        |

| Column address strobe | CAS       |

| Data input            | D         |

| Data input/output     | DQ        |

| Chip enable           | E         |

| Erasure              | ER  |

|----------------------|-----|

| Output enable        | G   |

| Program              | PR  |

| Data output          | Q   |

| Read                 | R   |

| Row address          | RA  |

| Row address strobe   | RAS |

| Refresh              | RF  |

| Read/Write           | RW  |

| Chip select          | S   |

| Write (write enable) | W   |

- Note 1: In the letter symbols for time intervals, bars over the subscripts, for example CAS, should not be used.

- 2: It should be noted, when further letter symbols are chosen, that the subscript should not end with H, K, V, X, or Z. (See clause 5)

- 3: If the same terminal, or signal, can be used for two functions (for example Data input/output, Read/Write) the waveform should be labelled with the dual function, if appropriate, but the symbols for the dynamic parameters should include only that part of the subscript relevant to the parameter.

# 5. SUBSCRIPTS C AND E (For Transition of Signal)

The following symbols are used to represent the level or state of a signal:

| Transition of signal                          | Subscript |

|-----------------------------------------------|-----------|

| High logic level                              | Н         |

| Low logic level                               | L         |

| Valid steady-state level (either low or high) | V         |

| Unknown, changing, or 'don't care' level      | 1 X 1     |

| High-impedance state of three-state output    | Z         |

The direction of transition is expressed by two letters, the direction being from the state represented by the first letter to that represented by the second letter, with the letters being as given above.

When no misunderstanding can occur, the first letter may be omitted to give an abbreviated symbol for subscripts C and E as indicated below.

All subscripts C and E should be in upper-case.

#### Subscript

| Examples                                                 | Full | Abbreviated |

|----------------------------------------------------------|------|-------------|

| Transition from high level to low level                  | HL   | L           |

| Transition from low level to high level                  | LH   | Н           |

| Transition from unknown or changing state to valid state | xv   | V           |

| Transition from valid state to unknown or changing state | VX   | <b>X</b>    |

| Transition from high-impedance state to valid state      | ZV   | V           |

Note: Since subscripts C and E may be abbreviated, and since subscripts B and D may contain an indeterminate number of letters, it is necessary to put the restriction on the subscripts B and D that they should not end with H, L, V, X, or Z, so as to avoid possible confusion.

# LETTER SYMBOLS FOR THE DYNAMIC PARAMETERS

### 6. SUBSCRIPT F (For Additional Information)

If necessary, subscript F is used to represent any additional qualification of the parameter such as mode of operation, test conditions, etc. The letter symbols for subscript F are given below.

Subscript F should be in upper-case.

| Modes of operation | Subscript |

|--------------------|-----------|

| Power-down         | · PD      |

| Page-mode read     | PGR       |

| Page-mode write    | PGW       |

| Read               | R         |

| Refresh            | RF        |

| Read-modify-write  | RMW       |

| Read-write         | RW        |

| Write              | W         |

# MITSUBISHI LSIS SYMBOLOGY

## FOR DIGITAL INTEGRATED CIRCUITS

| New symbol         | Former symbol       | Parameter—definition                                                                                                                                        |

|--------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  |                     | Input appositance                                                                                                                                           |

| D <sub>i</sub>     |                     | Input capacitance                                                                                                                                           |

| 0                  |                     | Output capacitance                                                                                                                                          |

| Pi/o               |                     | Input/output terminal capacitance                                                                                                                           |

| Ο <sub>i</sub> (φ) |                     | Input capacitance of clock input                                                                                                                            |

|                    |                     | Frequency                                                                                                                                                   |

| (φ)                |                     | Clock frequency                                                                                                                                             |

|                    |                     | Current—the current into an integrated circuit terminal is defined as a positive value and the current out of a terminal is defined as a negative value     |

| ВВ                 |                     | Supply current from V <sub>BB</sub>                                                                                                                         |

| BB(AV)             |                     | Average supply current from V <sub>BB</sub>                                                                                                                 |

| CC                 |                     | Supply current from Vcc                                                                                                                                     |

| CC(AV)             |                     | Avarage supply current from Vcc                                                                                                                             |

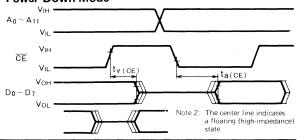

| CC(PD)             |                     | Power-down supply current from Vcc                                                                                                                          |

| DD                 |                     | Supply current from V <sub>DD</sub>                                                                                                                         |

| DD(AV)             |                     | Average supply current from V <sub>DD</sub>                                                                                                                 |

| GG                 |                     | Supply current from V <sub>GG</sub>                                                                                                                         |

| GG(AV)             |                     | Average supply current from V <sub>GG</sub>                                                                                                                 |

| 1                  |                     | Input current                                                                                                                                               |

| IH.                |                     | High-level input current—the value of the input current when $V_{OH}$ is applied to the input considered                                                    |

| IL                 |                     | Low-level input current—the value of the input current when $V_{OL}$ is applied to the input considered                                                     |

| он                 |                     | High-level output current—the value of the output current when V <sub>OH</sub> is applied to the output considered                                          |

| OL                 |                     | Low-level output current—the value of the output current when V <sub>OL</sub> is applied to the output considered                                           |

| loz                |                     | Off-state (high-impedance state) output current—the current into an output having a three-state capability with input condition so applied that             |

|                    |                     | it will establish according to the product specification, the off (high-impedance) state at the output                                                      |

| lozh               |                     | Off-state (high-impedance state) output current, with high-level voltage applied to the output                                                              |

| lozL               |                     | Off-state (high-impedance state) output current, with low-level voltage applied to the output                                                               |

| los                |                     | Short-circuit output current                                                                                                                                |

| Iss                |                     | Supply current from V <sub>SS</sub>                                                                                                                         |

| Pd                 |                     | Power dissipation                                                                                                                                           |

| N <sub>EW</sub>    |                     | Number of erase/write cycles                                                                                                                                |

| N <sub>RA</sub>    |                     | Number of read access unrefreshed                                                                                                                           |

| Ri                 |                     | Input resistance                                                                                                                                            |

| RL                 |                     | External load resistance                                                                                                                                    |

| Roff               |                     | Off-state output resistance                                                                                                                                 |

| Ron                |                     | On-state output resistance                                                                                                                                  |

| ta                 |                     | Access time—the time interval between the application of a specified input pulse during a read cycle and the availability of valid data signal at an output |

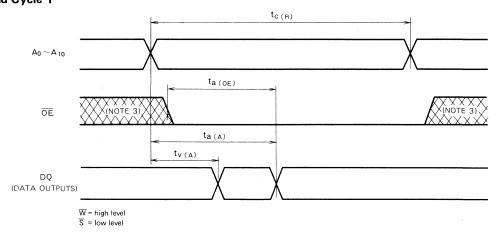

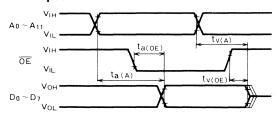

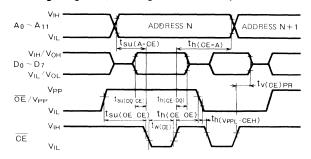

| ta(A)              | ta(AD)              | Address access time—the time interval between the application of an address input pulse and the availability of valid data signals at an output             |

| ta(CAS)            | 4(40)               | Column address strobe access time                                                                                                                           |

| t <sub>a(E)</sub>  | ta(CE)              | Chip enable access time                                                                                                                                     |

| t <sub>a(G)</sub>  | ta(OE)              | Output enable access time                                                                                                                                   |

| a(G)               | - ( /               | Data access time after program                                                                                                                              |

| a(PA)              |                     | Row address strobe access time                                                                                                                              |

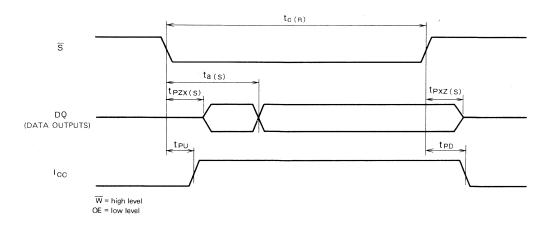

| t <sub>a(S)</sub>  | ta(cs)              | Chip select access time                                                                                                                                     |

| c (S)              |                     | Cycle time                                                                                                                                                  |

| CR                 | t <sub>c(RD)</sub>  | Read cycle time—the time interval between the start of a read cycle and the start of the next cycle                                                         |

| CR                 | t <sub>C(REF)</sub> | Refresh cycle time—the time interval between successive signals that are intended to restore the level in a dynamic memory cell to its original level       |

| topg               | t <sub>C(PG)</sub>  | Page-mode cycle time                                                                                                                                        |

| torg<br>tormw      |                     | Read-modify-write cycle time—the time interval between teh start of a cycle in which the memory is read and new data is entered, and the start of           |

| CHMW               | t <sub>C(RMR)</sub> | the next cycle                                                                                                                                              |

|                    |                     |                                                                                                                                                             |

| New symbol                                 | Former symbol           | Parameter—definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|--------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| t <sub>d</sub>                             |                         | Dubus tirrus, the tirrus harburen the englified reference actions as the control of the control |  |

|                                            |                         | Delay time—the time between the specified reference points on two pulses  Pelay time between clock pulses—e.g. symbology delay time clock 1 to clock 2 to clock 2 to clock 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| t <sub>d(φ)</sub>                          |                         | Delay time between clock pulses—e.g., symbology, delay time, clock 1 to clock 2 or clock 2 to clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| td(CAS-RAS)                                |                         | Delay time, column address strobe to row address strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| td(CAS-W)                                  | td(CAS-WR)              | Delay time, column address strobe to write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| td(RAS-CAS)                                |                         | Delay time, row address strobe to column address strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| <sup>t</sup> d(RAS-W)                      | Id(RAS-WR)              | Delay time, row address strobe to write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| tdis(R-Q)                                  | tdis(R-DA)              | Output disable time after read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| t <sub>dis(s)</sub>                        | tpxz(cs)                | Output disable time after chip select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| tdis(w)                                    | t <sub>PXZ</sub> (WR)   | Output disable time after write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

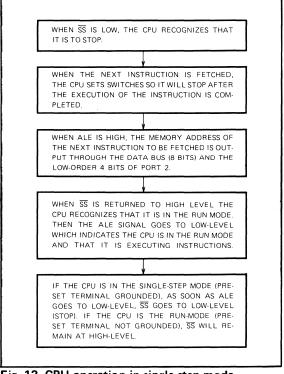

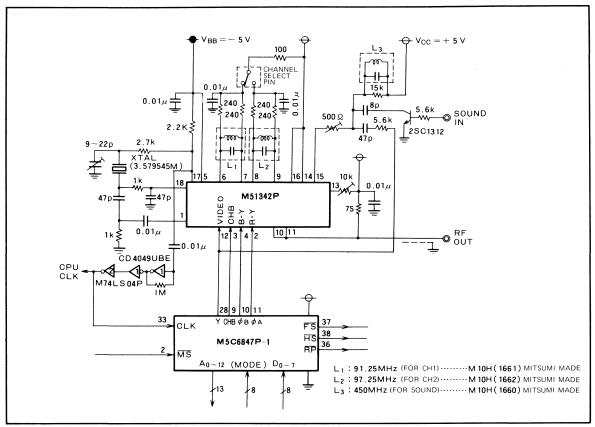

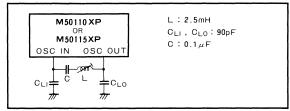

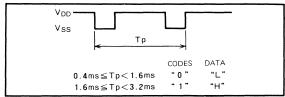

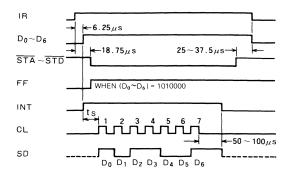

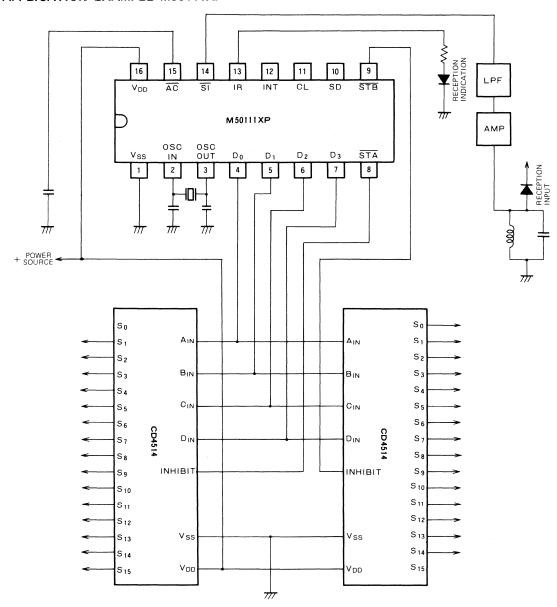

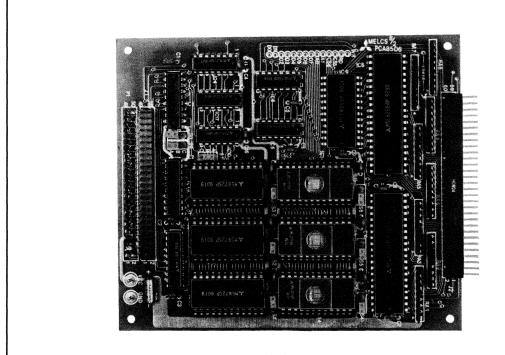

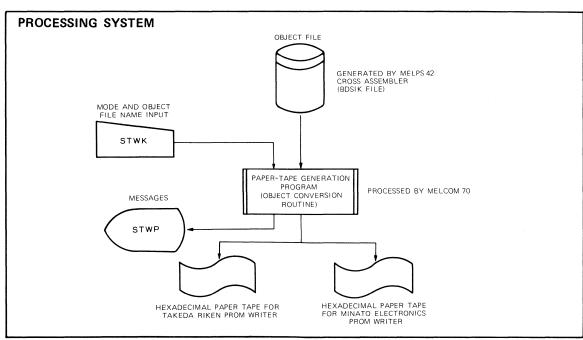

| tonL                                       |                         | High-level to low-level delay time the time interval between specified reference points on the input and on the output pulses, when the output to high-level delay time output is going to the low (high) level and when the device is driven and loaded by specified networks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |